基于Vivado千兆以太网口ILA核调试方案

本试验操作说明:

①软件平台:Vivado 2017.4

②硬件平台:FPGA A7 200T

③编程语言选择:VerilogHDL

④操作背景:基于该FPGA的千兆以太网口电路设计

1、网络与VIVADO代码配置:

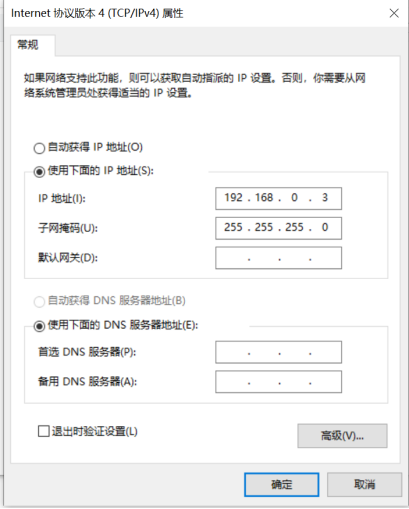

本测试案例中, 所用到的与PC连接的FPGA的IP地址设定为: 192.168.0.2

而PC电脑以太网本地地址所设置的IP地址固定为 : 192.168.0.3

设置方法如下图所示:

基本设置操作为:打开 ” 网络和Internet设置 ”, 选择以太网,选择更改适配器选项,选择以太网右键属性即找到上述设置IP地址。

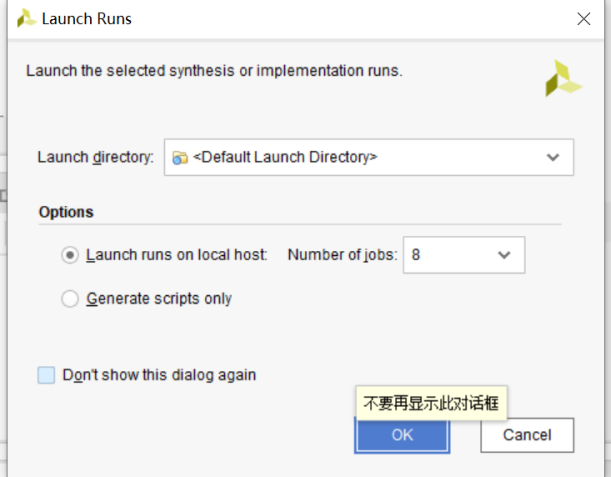

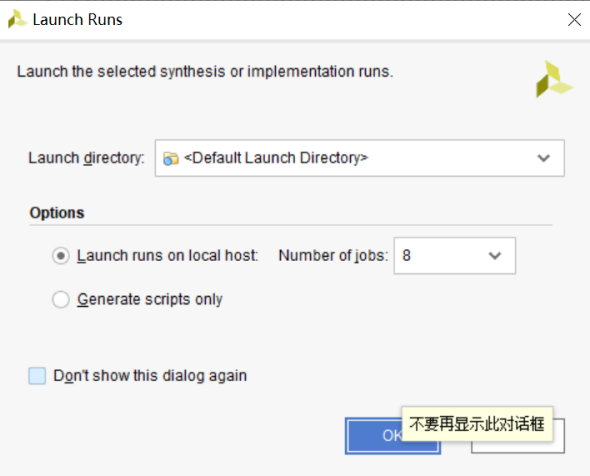

首先打开整个vivado工程后,即进行代码综合,如下图:

Vivado左侧综合选项“Run SYNTHSIS ” . 综合时的线程数可以选择最高,整体综合速度布局布线会加快。

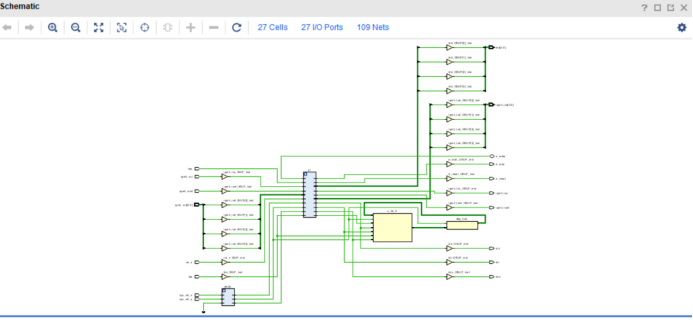

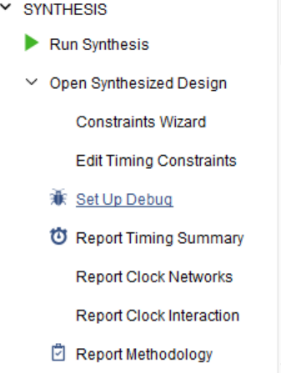

综合后,选择O penSynthesized Design 可以查看RTL图。而RTL图便于在众多的网口代码中,查看 数据流 。便于追踪传输的数据,经过哪些模块,经过了哪些RAM或者FIFO。

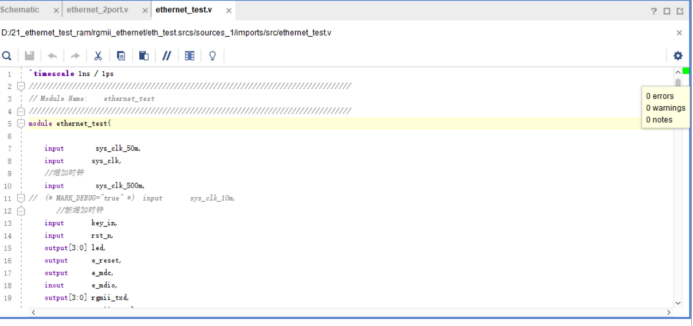

注意:代码如果右边有红色则代表代码语法有错误,黄色则是警告,绿色表示语法无错误。

如果语法无错误,综合时出错则会在下面信息中查看e rror 并点击相应模块可直接跳到对应有问题的地方。

这里面警告不影响比特流生成。语法均无红色警告。也不影响比特流生成。

2、连接FPGA与比特流文件烧写

首先选择生成比特流: Generate Bitstream

左侧最下方有生成比特流选项。

在这里线程数也可选择最高值,整体生成比特流速度会加快。

生成比特流之后需要连接开发板。

到此为止,比特流已经成功生成。下面就要连接开发板,把程序下载到开发板中。

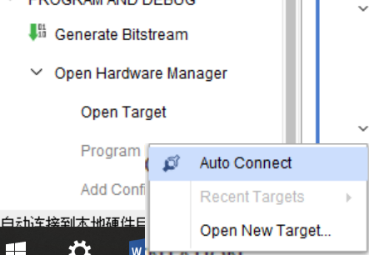

打开开发板电源,当LED灯呈现流水灯时候。点击O pen Target 的A uto Connect 连接开发板。

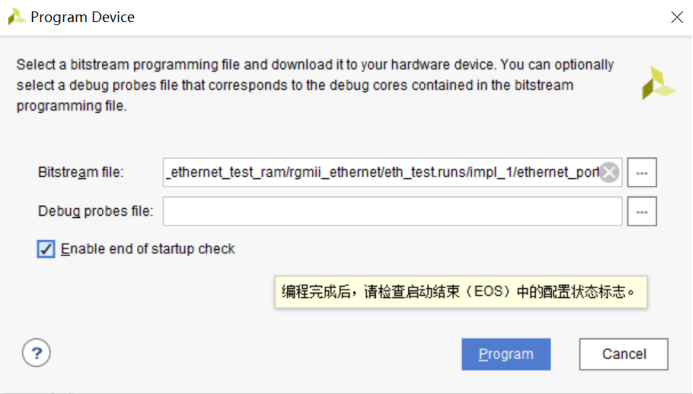

选择P rogram Device 的对应开发板型号选择。

点击p rogram 后,即把生成的比特流文件下载到开发板中。网口代码下载进去后。开发板灯 三个灯全部亮 时表示代码下载完毕,且网速为千兆以太网。两灯为百兆,单灯为十兆。

到此为止可以测试,是否PC与开发板网口连接已经接通。

具体操作为: 以管理员权限打开CMD窗口,输入arp –a查看ARP绑定结果,可以看到开发板的IP地址和MAC地址已经缓存。在CMD窗口中,输入ping 192.168.0.2查看PC与开发板是否ping通。

至此,可以确定代码已成功写入开发板。开发板与PC端以太网口已经接通。

3.vivado的ILA核调试

Vivado的debug功能主要是便于进行信号抓取,采样观察。便于分析数据流与控制流。

D ebug的功能有很多种方案,但是我们通常采用,先 ( MARK_DEBUG="true" ) 标记,再添加信号观察的方案, 此方法可以大大避免信号被优化的情况,同时也是操作最简单的方法。

首先在代码中,把需要观察的信号前面添加 ( MARK_DEBUG="true" )

如图所示:

把所要观察的信号前都要添加括号内容。添加后,确保程序语法无误后,进行 综合。

(每次添加完必须综合,系统自动生成debug的ILA核的XDC文件)

步骤如下:

第一步选择信号:

上图中,第一个选项就是咱们之前在代码中添加的debug信号。打开后可以看到所有 ( MARK_DEBUG="true" ) 标记过的信号,然后直接添加即可。我们这种方法选择 第一个选项 即可。

另外,第三个选项是移除debug核,选择后再综合,可以删除之前debug的ILA核。第二个选项是在这里直接添加信号。这样会有很多信号被优化,不推荐这个选项。

之后可以看到所有我们添加过 ( MARK_DEBUG="true" ) 这个语句的信号。右面Clock Domain 是 采样时钟 的选择。(右键后可以选择时钟)而左边的则是 观察的信号。

另外,如果左边选的观察的信号有时钟,则采样信号必须选择不同频率的时钟方可看到。通常采样时钟选择频率高的,而需要观察的时钟是低的。

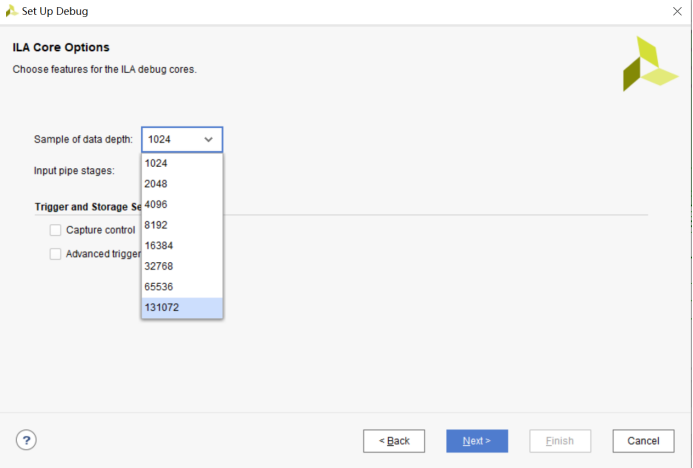

下一步就是设置 采样深度, 通常这个和和你观察的信号周期长度也有关系,如果信号变化需要较长的周期,设置深度也要设置的大一些避免采不到后面周期信号的波形。设置好之后,进行 综合 R un SYNTHSIS ,在这期间自动生成ILA核,综合后就开始生成 比特流 Generate Bitstream 。

生成 比特流 Generate Bitstream ,之后需要把文件下载到开发板中,不同于之前网口代码下载的是,因为我们要进行debug调试,则下载的文件一共有俩部分

第一部分是比特流文件,就是普通的生成的比特流文件。第二部分则是debug调试文件,也需要下载到开发板中。

这两部分的文件都需要下载到开发板中。

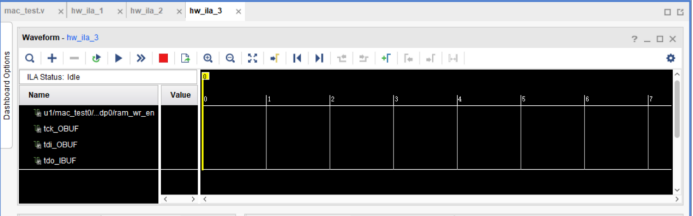

下载好之后会自动弹出,h w_ila 的波形框。

如果没有自动弹出,可以对设备进行刷新 Refresh device

弹出的框如果当时的debug所有信号采样时钟都是同一个时钟则只有一个h w_ila_1 。如果所有信号有俩不同的采样时钟,则会弹出h w_ila_1 和 hw_ila_2 。我本次的试验中有三个采样时钟所以弹出来了三个框,不过如果不是特殊要求,建议选择所有的信号为同一个采样时钟,这样可以在一个波形图中进行信号的对比观察。

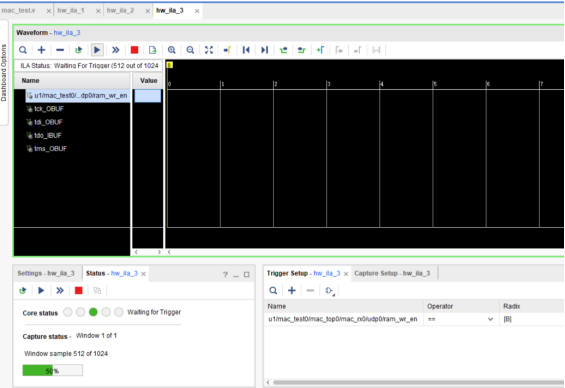

触发条件的选择通常都是选择 使能信号 作为 触发信号 。通常我们选择在数据流进入的RAM或者FIFO的写使能作为触发信号。在这里我选择了下行线路RAM的写使能。

选择RAM写使能的作用是,当且仅当,有数据从PC下发给开发板时,RAM写使能置高。设置 v alue=1 即变高时触发 。

左上角的“+”可以选择之前添加的信号,需要观察的信号添加到左边。

添加完成后点击“运行”就是那个三角符号。点击完运行后debug状态处于等待触发状态。

且左下角状态为5 0 %等待状态。

由于我设置的触发条件是写使能,所以只要下发数据即可触发。

打开网络助手,发一帧数据,就可以触发该条件了。

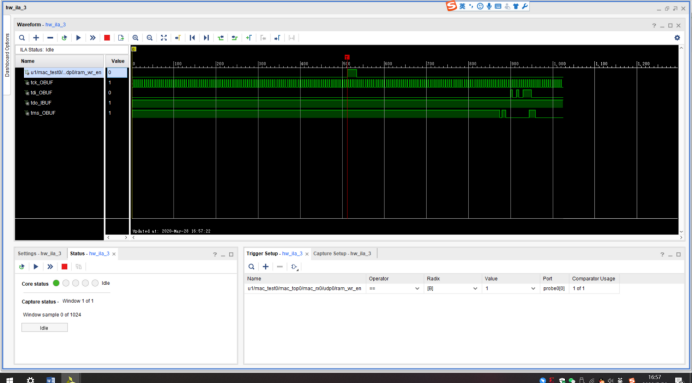

返回vivado可以看到。信号已经触发,需要观察的信号已出现波形。

Vivado的调用ILA核功能,就可以实时捕捉并观察信号的波形,这样根据周期与信号波形变化,可以对电路代码设计中的控制流与数据流向有较为深入的理解。从某种意义上来讲,ILA的信号捕捉功能与端子接口连接示波器的效果类似。但作为轻量级快速查看信号源与输出源,ILA核功能则方便许多。

如果觉得我的文章对您有用,请点赞。您的支持将鼓励我继续创作!

赞0作者其他文章

评论 0 · 赞 1

评论 0 · 赞 1

评论 0 · 赞 0

评论 0 · 赞 0

评论 0 · 赞 3

添加新评论0 条评论