基于FPGA的UDP/IP协议千兆以太网口设计

FPGA选型:XILINX A7 200T

实现模块:JTAG(用于测试)、千兆以太网口、上位机PC端labview界面

在这里注重讲千兆以太网口的实现过程

一、 UDP 协议数据包构成

下表为以太网帧格式整体划分:

前导码:8字节,连续7个8 ’h55 加一个8 ’hd5 ,表示一个帧的开始,用于双方设备数据的同步。

目的MAC地址:6字节,存放目的设备的物理地址,即M AC 地址

源M AC 地址:6字节,存放发送端设备的物理地址

类型:2字节,用于指定协议类型,常用的有0 800 表示IP协议,0 806 表示A RP 协议。

数据部分:共4 6 - 1500 字节,包含IP首部,2 0 字节。 UDP 首部8字节,应用数据X字节。

FCS:共4字节。

按照以太网格式划分:

第一部分:前导码 8 字节

深蓝色:前8个字节为前导码,8字节,占8个周期。

第二部分:以太网首部 14 字节

红色:目的MAC地址,6字节,占6个周期。

橘黄色:源MAC地址,6字节,占6个周期。

黄色:IPV4协议类型,2字节,占俩周期

第三部分:IP首部共2 0 字节

绿色:IP首部,2 0 字节,占2 0 周期

第四部分:UDP首部8字节

浅蓝色:UDP首部,8个字节,占8个周期

第五部分:应用数据(不限制数量,不发送为0,最多等于1 500 - 46 )

灰色:应用数据段不限制字节数量,整个以太网帧数据部分一共可以是4 6 - 1500 字节,最少是发送应用数据为空字节等于以太网首部1 4 +IP首部2 0 +UDP首部8+不发送数据0+帧尾4,等于 14 + 20 + 8 + 0 + 4 = 46 )

第六部分:帧尾占4字节

紫色:FCS帧尾4字节,占4个周期

上行数据帧格式研究整理:

周期序号起始于gmii_tx_en为高电平。直到gmii_tx_en变低结束。数据采用十六进制记录gmii_txd,严格对照以太网帧格式可以发现,下行与上行数据一样均保持严格的格式对照。 以太网帧格式的研究对随后进行网口数据流传输的分析起到了很大的作用。

经过推算可得,网络数据发不同的数据,以下是不同之处所位于的具体区域所在:

IP首段。

UDP首段。

应用数据段。

FCS帧尾

这些部分的周期会有所不同。

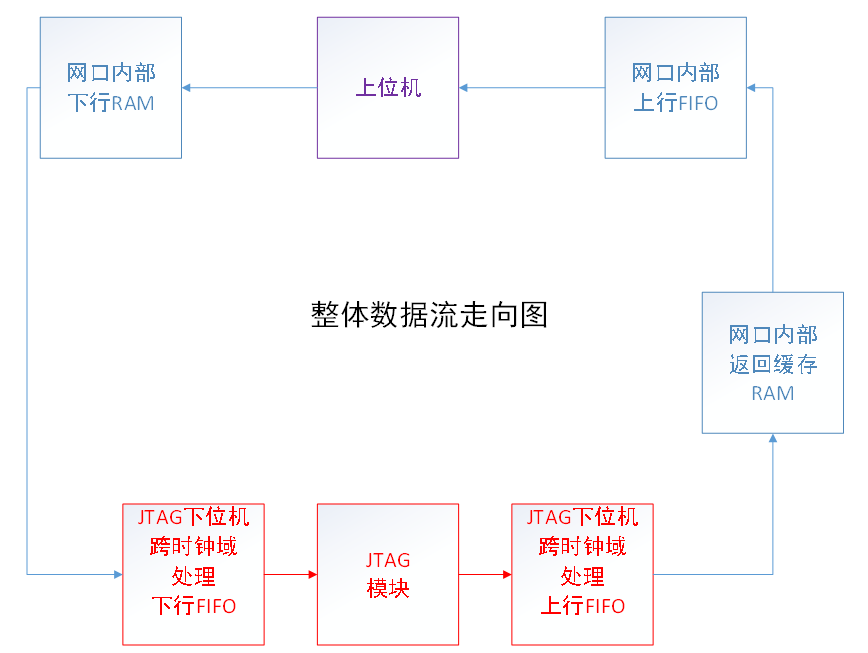

二、数据流

整体数据流向则为以下几个步骤:

- 从上位机发送数据,首先存储到网口UDP接收模块的RAM中。

2.然后读出数据给JTAG部分的下行跨时钟域处理的FIFO中,对使能信号与数据信号做跨时钟域处理。 - 处理后的数据给JTAG模块进行使用。并产生返回帧数据以及使能信号。

4.返回帧数据以及使能信号经过 JTAG 下位机跨时钟域处理后,产生的数据和使能返回给网口。 - 返回给网口的数据首先进入到缓存RAM中,缓存RAM通过地址和使能控制把数据写入,并且通过读地址增加产生读使能,返回给上行FIFO。

6.上行FIFO则把接收到的数据,返回给上位机。

总的来说,下行线路较为简单,通过从 udp_rx 模块中的RAM直接把数据经过跨时钟域处理后就读给下位机JTAG部分。而上行线路,通过跨时钟域处理后的数据首先进入到缓存RAM中,并且需要通过mac _ test状态机的控制逻辑,把数据存入到u dp_tx 模块的FIFO内。

网口内部的整体数据流向则为以下几个步骤: - 网口从上位机接收到的数据经过 MAC 层,然后由状态机控制传给IP层,再传给U DP 层。最后存储到 UDP 接收模块中的RAM中。

- 网口从下位机接收到返回数据后,首先存入到缓存RAM中,然后通过mac_test状态机的控制,把数据传输到U DP 发送模块中的F IFO 中。

3.发送F IFO 接收到数据准备好后,会向IP层发送请求,若IP层接收到请求如果可以接收数据,则反馈一个信号给UDP模块,UDP层将发数据到IP层。 - 同理IP层数据发送前也会向 MAC 层发送请求。如果M AC 层接收到该请求并允许接收后,反馈信号给IP模块,IP发数据到M AC 层。

三、控制流:

整体图说明:

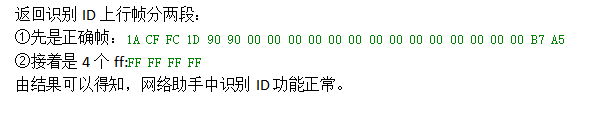

1.图中红色为JTAG部分。蓝色为网口部分。 - 该状态机分为两个部分,上电后ARP请求状态,以及UDP发送状态。这里我们主要对 U DP发送状态的核心状态及其信号进行解释说明。

3.接收RAM位于u dp_rx 模块中。数据和信号直接读出后经过跨时钟处理给下行JTAG模块。

缓存RAM位于mac_test模块中。接收来自JTAG跨时钟域处理后返回的数据及其信号。

发送FIFO位于udp_tx模块中。接收来自缓存RAM读出的数据同时写入FIFO中。

核心状态说明:

UDP发送状态为四个状态

WAIT---CHECK_ARP--- G EN_REQ---WRITE_RAM---WAIT

完整的UDP发送数据流程为如上状态跳转进行。

下行数据控制:

下行数据控制,是通过udp_ rx 模块中的RAM直接按地址把数据读出后,经过跨时钟域处理给JTAG即可。

读使能按照RAM读端口地址的增加而产生。而只要RAM写使能置高后,读地址延迟俩周期后开始增加。即RAM读地址 udp_rec_ram_read_addr <= udp_rec_ram_read_addr + 1'b1 。

与此同时,在读地址开始增加后,产生RAM读使能。 udp_ram_wr_en <= 1'b1 可以保证,读地址的增加和读使能增加是同时的。

从而产生的数据信号与使能信号的时序是对齐的。

上行状态控制:

M ac_test该模块主要控制数据的返回传输,图中蓝色的状态是上电后,首先发送ARP请求信号,直到对方回应,进入发送UDP状态。(此状态只发生一次)

发送UDP状态为图中红色状态。 wait状态时接收到从JTAG返回的数据进入网口上行链路的RAM,它的写使能有效,则判定它的发送数据信号有效。则将网口从JTAG接收到数据发送给上位机。每次发送前都要检查目的IP是否能在ARP缓存里找到,如果没有,则发送ARP请求。

状态机转移图:

⑤状态机分析

该状态机保证从下位机接收的J TAG 回传数据,通过FIFO返回给上位机,用的mac_test状态机控制,JTAG返回的信号需要进行跨时钟域处理,处理后的8位数据,使能信号,数据长度等信号会传送给网口模块。 M ac_test状态机会处理这些数据。

为了使接收和发送模块断开互不影响。需要隔断的信号为,上下行传输的8位数据,下行产生的读使能,上行写数据使能。返回数据的长度。

为了使数据信号与使能信号相位对齐,在上传数据时,mac_test模块中新添加一个RAM,该RAM接收端为下位机返回的数据,以及写使能。而读出的模块为读使能与读数据。读出后直接给udp_ tx 模块中的FIFO,并且按照网口协议打包上传。

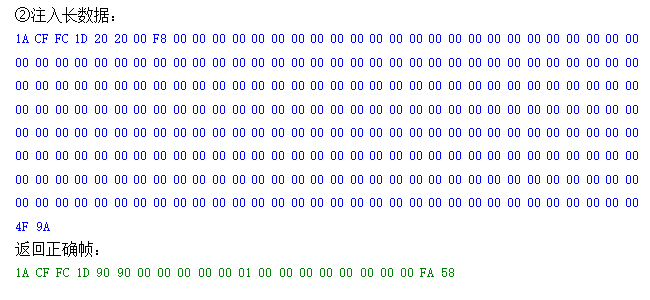

四、功能测试验证:

如果觉得我的文章对您有用,请点赞。您的支持将鼓励我继续创作!

赞1作者其他文章

评论 0 · 赞 1

评论 0 · 赞 0

评论 0 · 赞 0

评论 0 · 赞 0

评论 0 · 赞 3

添加新评论0 条评论