关于AIX系统命令 lssrad 输出的疑问

------ K1 Power 系统优化的资源亲和性问题分析

浪潮商用机器有限公司 技术支持部 李秀江

本文我们将探讨一下 AIX 系统命令 lssrad 输出,及相关输出字段的含义。

在日常系统维护管理工作中我们经常会用到 AIX 系统命令 lssrad ,该命令用于示系统 SRAD ID (调度程序资源分配域 ID )的层次结构和拓扑,通过它了解查看 CPU 和内存亲和性,进而指导我们进行相关的系统优化。在解释 lssrad 命令 输出时,尤其是对于关于 REF 项目 ,目前存在普遍的混淆。许多人将 REF 解释为 CEC ,但事实并非总是如此。下面我们将在这里用一个例子来解释它。在正式开始之前,我们先简单回顾一下为什么会出现 CPU 和内存的亲和性问题,并且在大型系统中我们要根据系统的配置和使用情况进行相关的优化。

正如我在上文开始时候提到的那样,有时内存不是在本地的,而是连接到不同的 POWER 芯片,当进程(程序)必须访问非本地内存时,它需要首先检查它是否未缓存在某个地方,如果没有,会请求从具有 RAM 内存控制器的 POWER 芯片读取它。 关于 POWER Cache Coherence (缓存一致性) 的议题我们有时间在单独介绍。

实际上,每个 POWER 芯片 都有一个内置于芯片中的所谓的结构总线控制器( FBC ),它的主要是用于与其他 POWER 芯片进行通信控制(比如查找缓存行)和传输(将缓存行移动到需要它的 POWER )。

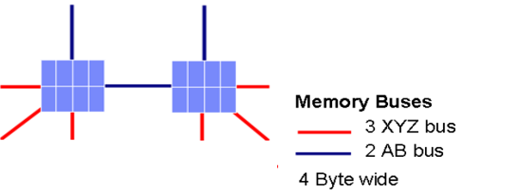

简单来说,有五种连接端口( fabric ports ),可以传输速率带宽分为 8 字节, 4 字节或 2 字节宽度。

这五个连接端口可以简单分为两个类型:

一类我们称之为 X Y Z 总线 : 这些总线用于企业级服务器,如 Power E880/850 和 E980/E950 中以直接连接同一 CEC 抽屉中的每个 POWER 处理器。

另外一类为 A B 总线 :这 类总线端口主要是用于低端系统也就是我们常说的 scale-out 服务器,用于 POWER 芯片到 POWER 芯片互联。在大型企业服务器中,如 Power E880 则用于连接四个 CEC 抽屉但是 E980 系统对此进行了改进和提升采用了 O bus 总线架构(参看图八)。

上面的说法是不是有点抽象呢,那我们可以简单的给大家画个示意图。

单个 POWER 芯片具有五条总线示意图:

每个 CEC 抽屉的高端机器 CPU 连接示意图:

低端机器使用 AB 总线进行连接示意图:

在只有少数 POWER 芯片的 scale-out 系统中(一个或两个物理芯片),是不需要更高的带宽进行连接的,因为远程处理器计算很少,这也意味不会有跨系统主板 (motherboard) 的处理和调用 。但是在在高端机器上也就是 sclae-up 系统中,远程处理器的使用机会会呈指数级增长,因此它们需要具有完整的 8 字节总线( XYZ 加 AB )来最大化带宽,这也很好的解释了我们在高端机器上具有出色的扩展性的一个原因。 也 因此带来了高端 sclae-up 系统上就会涉及到 POWER 芯片与内存调度使用的亲和性问题。(本文不探讨具体的 CPU 和内存的亲和性问题)。

以上图片是我们做了一个简化版的 CPU 的介绍,真实的 CPU 架构远远比这个复杂的很多。个位可以参考如下的 POWER9 CPU 架构图脑补一下真实的微电路世界。

接下来我们继续我们的话题。如下是一台 IPS K1 Power S824 系统。这是一个可以配置 24 个内核的 2 插槽系统,通常我们把它看做是一个单一的 CEC 。

我们这个 S824 上创建了一个共享 LPAR , 它使用 13 个内核(即 13 个物理处理器核心),并且启用了 SMT 2 ,这意味着我们将有 26 个逻辑处理器,这 26 个逻辑处理器在这个系统的命名上是从 0 到 25 (不一定是按顺序排列)。

关于此分区 LPAR 的 lssrad 命令详细 输出如下:

lssrad -av

REF SRAD MEM CPU

0

0 5921.88 0-1 4-5 8-9 14-15 20-21

1 5974.94 2-3 6-7 12-13 18-19 24-25

1

2 3715.56 10-11 16-17 22-23

从上面的这个输出结果可以告诉我们 REF 列 有 REF0 和 REF1 两个,但是 S824 只是一个 CEC 系统,它没有额外 CEC 柜子,问题出在哪里呢?这个就是大家经常疑惑的地方。

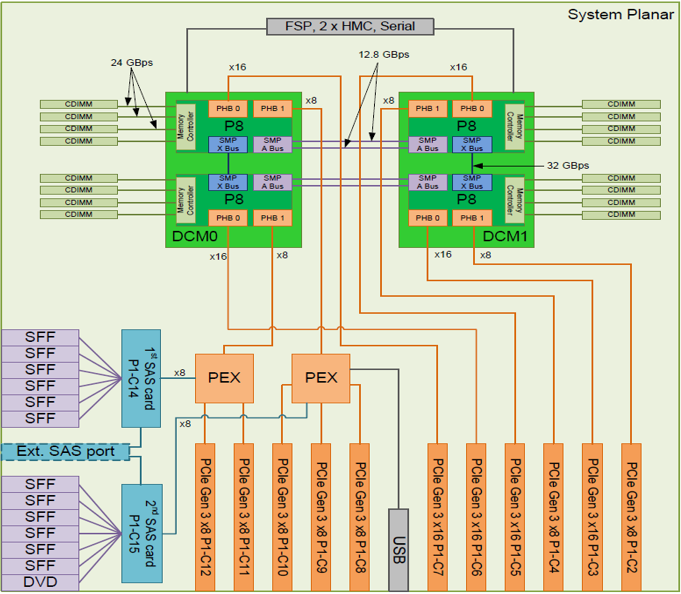

因为按照通常理解,一个 CEC 就代表了一个 REF 列 , 而上面的输出在 REF 列下面有 0 和 1 ,通常我们会认为是两个 CEC ,分别是 CEC0 和 CEC1 即该系统有两个 CPU 系统单元柜子。实际上该系统其实就是一个 S824 。为什么会这样呢?下面我们将结合 S824 的相关架构图来进行解释:为什么 REF 列有多个输出。如下是 S824 的 12C 双 CPU 系统架构图:

在这个 S824 系统中具有 2 个 CPU 模块,每个 CPU 模块又包含了 2 个 Power8 芯片模块,因此这些模块称为双芯片模块( DCM )。该系统上的每个 Power8 芯片都有 12 个内核,所以它总计是一个 24 核心系统。

现在,让我们仔细看看每个 Power8 芯片是如何互连的。在上面的架构图中我们可以看到在 CPU 模块内部,它们使用 X 总线连接, X 总线是具有 32GBps 速度的总线,为快速总线。但是在两个 CPU 之间,两个 Power8 芯片使用 A 总线连接,这是一种速度为 12.8GBps 的慢速总线。从根本上说, POWER 处理器有 2 种总线用于互连,一种是用于连接到近距离,另一种是通常用于跨 CEC 连接到远距离。但是在这个特定的系统中,在同一个 CEC 中, 2 个模块使用慢速总线 A bus 进行了互连,这也是为什么每个 CPU 模块的资源通过 lssrad 命令显示为两个不同的 REF 的原因 。

那么有关 Power E880 的单个系统节点(单个 CEC )又是什么样的连接架构呢?大家可以参考以下 E880 的系统平面图:

在这里,每个模块中都有一个 Power8 芯片(即单芯片模块或 SCM ),并且这 4 个 CPU 模块之间使用更快的 X 总线互连,因此如果我们用 lssrad 命令进行相关查询,该 CEC 的所有 CPU 都将通过 lssrad 显示为单个 REF 。在这里, A 总线将离开 CEC 用以连接外部 CEC 上的 CPU 进行互联。

如果有相关设备环境的话,大家可以在自己的系统上用命令行验证一下相关结果,因为没有 E880 的测试环境,我这里没有办法给大家提供相关的输出内容。

那么对于 K1 Power E980 的单个系统节点(单个 CEC )又是什么样的连接架构呢,大家可以请参阅如下系统平面图,前面我们提到了 E980 跨 CEC 是采用了更高速的 O bus 总线 。

希望大家现在都理解了 REF ,接下来让我们来看看 SRAD ( Scheduler Resource Affinity Domain )

影响操作系统调度程序最重要的资源是内存和系统处理器,每个处理器芯片都有内存控制器和关联的内存。在上面的系统平面图中大家可以看到 CPU 与内存的的连接架构图。每个 Power 处理器芯片都有多个内核和关联的内存,这组紧密的核心和内存称为 RAD ( Resource Affinity Domain )或资源亲和域。而调度程序就是这些资源的管理员,我们将其称为调度程序资源关联域( SRAD )或者称为调度程序资源分配域。

现在大家都已经明白了, lssrad 在的输出 SRAD MEM 和 CPU 下显示的内容了。

lssrad -av

REF SRAD MEM CPU

0

0 5921.88 0-1 4-5 8-9 14-15 20-21

1 5974.94 2-3 6-7 12-13 18-19 24-25

1

2 3715.56 10-11 16-17 22-23

基于上面的 lssrad 输出,该 LPAR 具有来自 SRAD0 和 SRAD1 的 10 个内核 /CPU (因为是 SMT 2 所以 总计就是 2 0 个逻辑 CPU 即: 0-1 4-5 8-9 14-15 20- 21 2-3 6-7 12-13 18-19 24-25 ), 以及来自 SRAD2 的下的 3 内核(因为是 SMT 2 、 总计有 6 个逻辑 CPU 即 10-11 16-17 22-23 ) ,前者 属于 REF 0 对应 SARD 0 和 1 ,后者属于 REF 1 , 位于对应 SRAD 2 。

关于内存和 CPU 的亲和性。该系统总计具有来自 SRAD0 的 5921.88MB 内存,和来自 SRAD1 的 5974.94MB 内存以及来自 SRAD2 的 3715.56MB 内存。

让我们看看此 LPAR 的 CPU 与内存比率是多少?

SRAD0 中每核 5921.88 / 5 = 1184.38MB 内存, SRAD1 中每核 5974.94 / 5 = 1194.988MB 内存, SRAD2 中每核 3715.56 / 3 = 1238.52MB 内存。因此,此 系统的 lssrad 输出告诉我们分配给此 LPAR 的 CPU 与内存比率约为 1GB ,并且平衡良好。

由于 REF 是非常令人困惑的部分,从上面的分析我们可以得出结论,所有由更快总线连接的 SRAD 都包含在一个 REF 中, 那么 Power E880 或 Power E980 中的 REF (参阅其上面的系统平面图片)最多可以有 4 个 SRAD 。

好了,不知道大家理解了没有,如果大家有环境可以在自己的环境下进行相关的验证,我们下期再见。

如果觉得我的文章对您有用,请点赞。您的支持将鼓励我继续创作!

赞0

添加新评论0 条评论