K1 Power主板PCB的黑科技

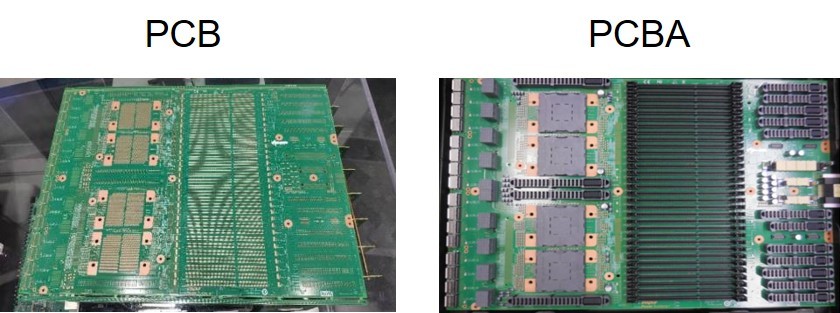

PCB 全称是 Printed Circuit Board ,也就是我们常说的印刷电路板。与 PCB 一起经常出现的另一个词是 PCBA ,即 Printed Circuit Board Assembly 。两者的区别是 PCB 上没有任何电子元器件, PCBA 则是以 PCB 为原料,向 PCB 上安装了元器件后的成品。下图是 K1 Power 主板 PCB(左) 和 PCBA (右)。

从俯视图上看, K1 Power 主板 PCB 与一般服务器主板 PCB 没有什么大差别,但 K1 Power 主板 PCB 内部可是满满的黑科技。

一、材料

任何电子产品中,元器件都需要载体, PCB 就是这样一个载体,并还用导线将元器件依照电路原理图连接在一起。所以 PCB 有两大功能:支撑和互连,而它的两大主要组成成份 -- 基板和铜箔分别为实现这两大功能提供支持。

在当前技术条件下,大多数电子产品 PCB 基板都采用由高分子合成树脂和增强材料组成的绝缘层板。由于玻璃纤维具备高刚性、低热胀率、和低变形量等特点,在 IT 产品中被普遍用来充当增强材料,这种使用玻璃纤维编织形成的平面材料被称为玻璃纤维布。

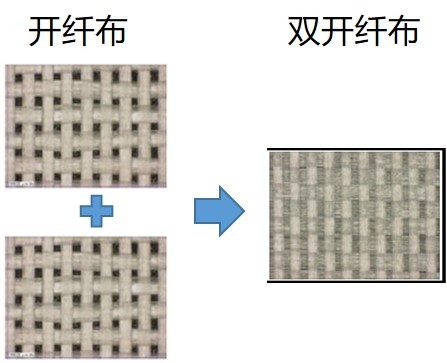

玻璃纤维布采用与织毛衣相似的编织工艺制造,它的好处是结构稳定,缺点是纤维之间不可避免地出现缝隙。从下图左侧两块玻璃纤维布放大图就可以看出,灰色条带是玻璃纤维,黑色部分就是缝隙。现代制造工艺中会使用开纤技术将玻璃纤维扁平化以形成开纤布,开纤布的玻璃纤维从原有的圆形被压扁以缩小纤维之间的缝隙,但这一工艺还是无法完全消灭缝隙。

开纤布浸润树脂后,缝隙会被树脂填充,成为平滑的基板。低频信号在这种基板之上运行正常,但是传输的是高频信号时,就有可能出现问题。 PCB 中传输信号的铜箔覆盖在基板之上,如果一条铜箔下方的基板有缝隙,因为树脂和玻纤布的电气特性完全不一样,铜箔传输的信号受其电气特性影响,传输速度会发生变化,信号本身也会出现衰减。这就好比铁路,开纤布是路基,铜箔是铁轨,火车就是信号。如果路基是一段硬土一段软土,不是按统一的标准铺设,虽然有铁轨,但火车的行驶还是会受到路基的影响不能运行太快,否则坐在火车里的人会感觉车体在上下颤动而不舒服。为了将此类影响降到最小, K1 Power 采用双开纤布,也就是用两张开纤布叠加,把缝隙盖住,这样保证了传输线下方是同样的介质,达到抑制信号衰减的效果。

PCB 的互连功能是通过在基板上覆盖导电率较高、焊接性良好的纯铜箔来实现。 K1 Power PCB 使用的铜箔也非常有讲究。几乎每层覆铜都是 1 盎司。这是指 1 平方英尺面积上平均铜箔重量是 1 盎司,也就是 28.35 克。我们知道,铜密度是每立方厘米 8.9 克, 1 平方英尺等于 929 平方厘米。不难算出每层铜箔厚度 =28.35( 克 )/8.9( 克 / 立方厘米 )/929 平方厘米 =0.003429 厘米 =34.29 微米,业界一般简化地称之为铜厚 35 微米。

PCB 上铜箔线其实就相当于元器件之间的连接线,它的截面积与之能通过的最大电流是直接相关的。在相同线宽前提下,铜箔厚度越厚,能够承受的电流也就越大。

K1 Power PCB 几乎每一层都使用 35 微米铜厚,这样做并不是因为 K1 Power 工作时的电流大,而是为了保证系统可靠性。在同样材料的 PCB 板上,每条导线能承受的最大电流除了和导线的截面积有关外,还会受到焊盘和过孔的影响。焊盘和过孔因为过锡后增强了其对电流的承载值,但焊盘与焊盘之间线路的最大电流承载值依然是导线宽度允许最大的电流承载值,如果电路瞬间发生波动,且波动范围超过了原有线宽所能承受的电流范围,焊盘不会受到影响,可焊盘与焊盘之间的线路就很容易烧断。 K1 Power 在所有板层都使用至少 1 盎司的铜箔,在电源层更是有 2 层分别使用了 2 盎司的铜箔,可以完美应对上述情况的发生。

与之相比,一般 x86 PCB 板的内层是用 1/2 盎司或是 1/3 盎司铜箔,而外层才用 1 盎司。事实上,整个业界除了一些大功率或者高压专用设备外,很少有 IT 产品使用 3 盎司及更大覆铜量的 PCB 。 K1 Power 是真正的业界良心!

当把 PCB 比喻成铁路时,双开纤布的使用决定了地基结构,铜箔的厚度规范了铁轨尺寸,但为了保障火车的正常运行, K1 Power 还优选了地基和铁轨的材料。

对于高速 PCB 而言,保障信号完整性最有效的方法就是减小信号传输损耗。根据电磁场和微波理论, PCB 传输损耗主要由介质损耗和导体损耗两部分构成。介质损耗受基板材料影响,由于构成板材的玻璃纤维布和树脂等绝缘材料介质的带电粒子被束缚在分子中,外加电场会使其产生微观位移,使介质中的偶极子随电场方向规则排列,这一现象被称为介质的极化。极化过程产生的能量损失就是介质损耗,业界用板材的 Df 值(耗散因子)来衡量介质损耗的大小并将板材分为多个等级:

为了保障 K1 Power 产品的信号完整性, K1 Power 选用了 Very Low Loss 等级的板材,这种板材与 x86 服务器普遍使用的 Low Loss 板材相比价格高 3.6 倍。

PCB 传输损耗中的导体损耗是由于导体存在损耗电阻,在电流通过时发热引起的,其主要影响因素是导体的电阻、电流分布(趋肤效应)和导体表面粗糙度。其中,导体的电阻由导线的金属元素特性决定,趋肤效应引发的热损耗随传输频率的增加而增大,这两项都难以改变,所以导体损耗主要由导体粗糙度决定。当粗糙度越大,信号传输时产生的驻波和反射等越大,信号损耗越大。

按粗糙度不同, PCB 常用的铜箔有低轮廓铜箔( HVLP 铜箔)、反转铜箔( RTF 铜箔)和高延伸性铜箔( HTE 铜箔)。从不同类型铜箔切片和毛面 SEM 图片可以看出, HVLP 铜箔毛面的表面形貌起伏落差小于 RTF 和 HTE 铜箔,其粗糙度远小于 RTF 和 HTE 铜箔。 K1 Power 为了减少导体损耗自然是不计工本地选择了低损耗的材料。

二、设计

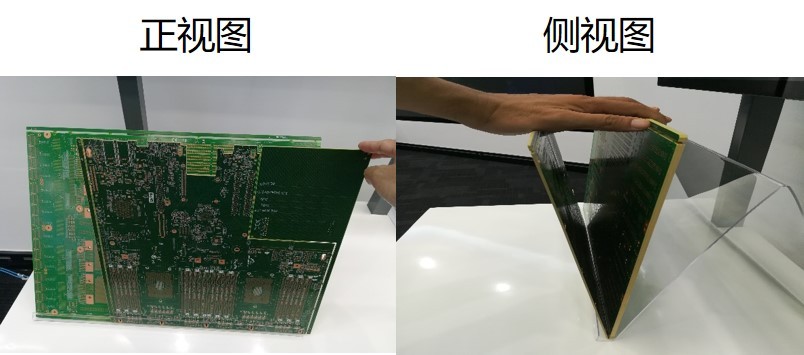

K1 Power PCB 的用料从外观上看好像并不特殊,但是它的厚度与普通服务器 PCB 可是有很大的不同。

上图是 x86 服务器和 K1 Power 服务器的主板 PCB 对比。从图中可以看到,两个 PCB 从正面看区别不大,但是在侧视图里,右侧的 K1 Power PCB 要明显比左侧的 x86 PCB 厚得多。

对于 x86 服务器来说,主板 PCB 不会超过 18 层,但 K1 Power E980 主板 PCB 是 40 层!

我们知道,两点之间直线最短,为了保证两个元件之间的信号传送,这两个元件管脚之间最好是用直线连接。可惜在大多数 PCB 上,由于管脚分布、过孔、以及走线空间等因素,两点之间直线连接布线几乎是不可能。但当 PCB 上电路保持不变时, PCB 层数增多,每层信号线数量就会越少,每层布线时顾虑也就会减少,两点之间连接就越有可能用更短的线路实现。

PCB 在布线中使用更短连接线带来的最大好处是保障信号完整性。在当前电路设计里,差分信号的应用越来越广泛,电路最关键的信号往往都要采用差分结构设计。差分信号,通俗地说,就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态“ 0” 还是 “1” 。承载差分信号的那一对信号线就称为差分线。差分信号和普通单端信号走线相比,最明显的优势体现在以下三个方面:

- 抗干扰能力强。因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,接收端关心的只是两信号的差值,外界的共模噪声可以完全被抵消。

- 能有效抑制电磁干扰。同样的道理,由于两根信号极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。

- 时序定位精确。差分信号对时序的判断是基于接收端两根线上信号幅值之差发生正负跳变的点,而不像普通单端信号依靠高低两个阈值电压判断,因此受工艺、温度的影响小,能降低时序上的误差。

差分走线虽然优势很明显,但是其缺点也是很明显:两根差分走线必须要等长。可是当一个布线层上线路非常稠密时,两根差分线很难完全平行,必须通过适当绕线才能达到线长匹配。当线路稀疏时,等长的平行布线就相对更容易实现,保证了信号完整性。

另外,当层数增多后,一些有可能对其它信号产生干扰的信号源就有可能被放置到单独一层上,通过层与层之间的屏蔽减少信号之间串扰,进而保证信号稳定性和可靠性。

上图是 K1 Power E980 主板的 PCB 截面示意图,从图中可以看出, K1 Power 主板中间部分是电源区域,两侧是高速信号区域。图中橙色代表的是铜箔,在高速信号区,橙色是高矮相间,高的代表地层,矮的代表信号层,也就是说 K1 Power 每两层信号之间都有地层作为屏蔽。这使得任意一层信号都拥有上下两层的电位参考平面,而 K1 Power 正是通过双参考平面设计更好地实现了对电磁干扰的屏蔽,避免信号产生串扰。

与之相反,很多 x86 服务器的主板设计就没有这么讲究。在这些 x86 服务器的 PCB 中,厂商为了节省成本,会在两个地层中间放两个连续信号层,这被称为双带线技术。在双带线情况下,信号线不仅有同层串扰,还会有相邻层串扰。虽然厂商在设计时会尽量考虑将邻层水平方向上的距离拉开,但层与层之间的串扰还是难以避免,并且事实证明相邻层的串扰会比同层的串扰要严重。而 K1 Power 显然不会为这一点小利去拉低产品可靠性。

三、工艺

多层 PCB 板的加工一般要经过内层线路、层压钻孔、金属化孔、外层线路、表面处理等 5 个主要工序。 K1 Power 主板的 PCB 是 40 层,虽然这为保证信号完整性、防止串扰等方面提供了保障,却对生产工艺提出了更高的要求。

我们都知道,多层 PCB 板是由多层导电图形层与绝缘材料交替层压粘在一起制成的印刷电路板,这种制造工艺势必造成两种偏离的产生。

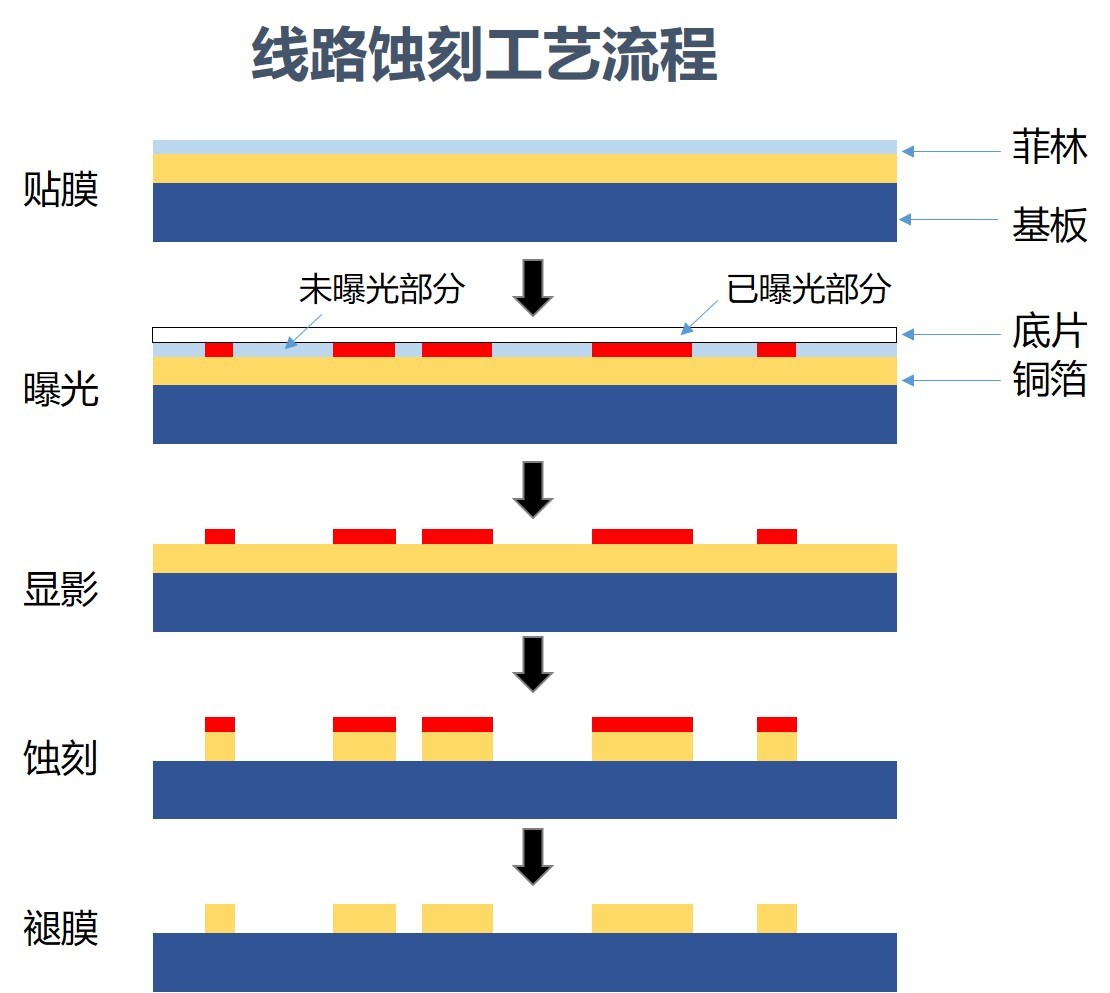

首先是内层层偏。 PCB 板每个导电图形层在最开始都是一张完整的铜箔,加工时,先在铜箔之上覆盖一层菲林,然后使用曝光机,将紫外线通过底片使菲林上图形部分感光,将底片上的图形转移到铜板上。再通过显影将未曝光部分的菲林去掉,仅留下通过底片转移过来的已曝光菲林,最后使用蚀刻技术将铜箔上没有菲林覆盖的部分腐蚀掉,只留下最后的线路。在这一过程中,不同曝光层次的菲林涨缩不一致、曝光机对位偏移、人员操作不当等因素都会导致内层层偏。

除了内层层偏以外,还会出现压合层偏。在压合之前,每层之间要加入半固化片( Pre-pregnant , PP 片),这是一种由树脂与载体合成的片状粘结材料,实现层与层之间的绝缘与粘接。在压合过程中,半固化片先会融化,成为液态填充进被腐蚀掉的铜箔之间,然后进一步加热后逐步固化,形成稳定的绝缘层,同时将相邻两层连接成一个整体。在半固化片变为液态后,层与层之间有可能发生滑动形成层偏。另外,各层芯板涨缩不一致、定位孔不良等原因也会导致层偏。

不论是内层层偏还是压合层偏,层偏的方向都是随机的,发生层偏的相邻两层之间走线的水平距离有可能会被缩小,层间的串扰增大。而如果发生层偏的部位有过孔和焊盘,那么因为层偏的存在,这些过孔和焊盘的连接会对信号产生阻抗波动,最终造成信号衰减。

为了尽量减小层偏对信号的影响, K1 Power 的 PCB 加工标准比 x86 要严格得多。这种高要求使得成本增加,显而易见,这些成本的增加并没有挡住 K1 Power 追求极致品质的步伐。

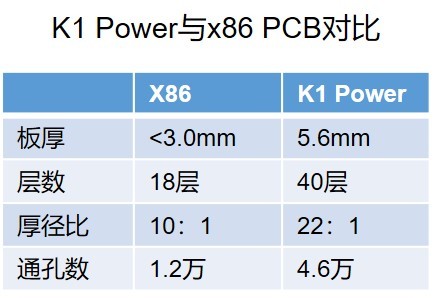

根据 PCB 加工工序,压合之后就要进行钻孔。但在 K1 Power 主板 PCB 上钻孔还真没那么容易。 K1 Power 主板 PCB 板的厚度已经达到了 5.6mm ,而元件器管脚直径与 x86 服务器上的是一致的,最小孔径都是由 CPU 针脚决定,是 10mil (密耳, 1 密耳 =0.001 英寸 =0.0254 毫米) , 于是钻孔的厚径比为 22:1 。与之对应,普通 x86 服务器的主板厚度小于 3 毫米,厚径比只有 10:1 。

大厚径比对钻孔工艺提出了非常高的要求。在用钻头钻孔时,钻头根据水平转速和向下推进速度的不同,会呈现韧性和刚性两种特性。这两种特性是互成反比的,韧性越大,刚性越小;反之,刚性越大,韧性越小。

韧性大时,一方面钻头工作时会发生倾斜和偏移,有可能钻到旁边的走线,导致短路;另一方面钻头有可能引起 PCB 板抖动而产生变形,撕裂铜箔,形成断路。

刚性大时,钻头钻得越深,受到的压力就越大,容易发生断钻情况。

一张 K1 Power E980 主板 PCB 上一共有约 4.6 万个过孔,无论是短路、断路、断钻、还是变形,只要发生一处,就会造成整张 PCB 报废,所以在加工 K1 Power 主板 PCB 时不仅对钻头的刚性和韧性有很高要求,而且为了保证加工精度还需要避免使用磨损的钻头,也就是说在很多情况下即使钻头还可以使用,但因为其锋利程度下降,也不能用于 K1 Power 主板 PCB 加工,而不得不被更换,导致加工成本直线上升。

打孔之后就要对整个 PCB 板进行电镀处理,以便在最外层和过孔内径上沉铜。电镀铜最常用的工艺是直流电电镀。但在直流电镀时,过孔入口处有尖端放电效应,导致孔口电流密度较高,孔内电流密度较低,于是孔中心镀层厚度与板面镀层厚度差别很大,孔中镀层厚度两端厚中间薄,出现 “ 狗骨头 ” 模型(如下图)。

由于 K1 Power PCB 的厚径比是 22:1 , “狗骨头”效应就更加明显。为了避免“狗骨头”, K1 Power 采用了脉冲电镀工艺。在电镀过程中,电流在每秒钟内正反向切换很多次。一个周期的作用时间里,正反向时间比是 20ms : 1ms ,即正向作用 20ms 时间后,电流切换成反向作用 1ms 。在反向作用期间,反向脉冲幅度通常大于正向脉冲,大幅度、短时间的反向脉冲导致电镀添加剂有机物分子从板面脱附开来。高电流密度电镀效率高,加速剂分子在高电流密度区脱附快于低电流密度区,作用结果就是高低电流密度区镀层更加均匀。其代价是成本增加。

使用脉冲电镀只是解决了孔壁的厚度问题,但没有解决电镀层的连接强度问题。由于铜和基材是不同的材料,在后继热处理时会因为基材与孔壁铜热膨胀系数存在差异产生拉扯力,一旦孔壁铜与基材之间的结合力无法对抗这种拉扯力,就会出现孔壁分离。而 K1 Power 主板 PCB 的厚径比高达 22:1 ,这种现象就更加明显。

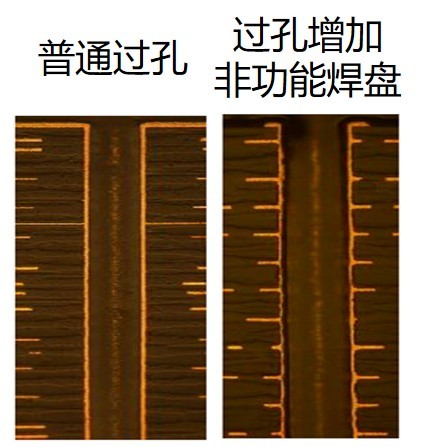

为了解决孔壁分离问题, K1 Power 采用了非功能焊盘以增加过孔连接层。但是在设计时需要区别对待高速信号和非高速信号,非功能焊盘会增加过孔的寄生电容,导致高速信号损耗增加。为了保障信号完整性,所有与高速信号有关的非功能焊盘全部做删除处理。而对非高速信号,纵向间隔 15mil (约 0.38 毫米)左右保留非功能焊盘。

仅仅处理孔壁分离问题对于追求完美的 K1 Power 来说还是不够。在 PCB 中,大多数过孔只连接某几层,但是钻孔是从第 1 层通到第 40 层,这样在镀铜之后,孔铜中的一段铜完全无用。比如需要将第 1 层连到第 16 层,从第 16 层一直到第 40 层这部分铜箔是完全不需要。事实上,这部分不仅无用,而且有害。当高速信号从第 1 层传输到第 16 层时,有一部分信号会按照设计沿着第 16 层的铜箔横向传输,不过还有一部分信号会继续沿着孔壁向第 40 层传输,并在传输到第 40 层后发生反射,对原有信号进行干扰。为了尽量保证信号完整性, K1 Power PCB 上采用了大量的背钻,就是用比原有孔径大一些的钻头,在原有的孔上把多余的铜箔再去掉。

按照制板工序,再往后就要对外层铜箔进行蚀刻,但在蚀刻时不能只保护外层的线路,还要在蚀刻前对线路板镀锡来保护通孔内的孔铜不被腐蚀掉。在电镀过程中又碰到了高孔径比问题,孔径中间部分有可能会没被锡所覆盖,或者即使被覆盖,也有可能无法满足镀锡厚度 4um 的要求,如果在这种情况下进行外层线路蚀刻,很有可能穿孔内的铜箔也会受到影响。

为了保证产品质量,把所有隐患扼杀在摇篮阶段, K1 Power PCB 在镀锡后还要增加负片制板流程,也就是在最外层不能被蚀刻的铜面上覆盖一层负片干膜。对于穿孔而言,覆盖在之上负片干膜相当于给一口井盖上了井盖,断绝了蚀刻药水向穿孔内渗透的途径,保证了 PCB 质量

复杂、先进、以及高标准的加工工艺使得 K1 Power PCB 对生产加工厂商也提出了非常高的要求。在 K1 Power 投产之前,国内所有 PCB 厂商都没有超过 30 层 PCB 的加工经验,大多数厂商在看到 22:1 的厚径比这一指标后就直言能力不足,最后仅剩为数不多的几家高端厂商能够入围进行生产测试。即使是这些厂商,依然有些在生产能力指标都能满足 K1 Power 要求的前提下,在测试阶段还是发现成品率过低而主动退出。由此可见 K1 Power PCB 的科技含量非常高!

四、测试

PCB 板生产完成后,还要进行严格的测试。 K1 Power PCB 与普通的 x86 PCB 明显不同的就是 IST (Interconnect Stress Test) 测试。这是一项对 PCB 成品板进行互连结构完整性的测试,可以对基板材料、内层间的结合、孔壁铜与基板结合等各方面进行检测,从而对 PCB 板的可靠性给出客观评价。

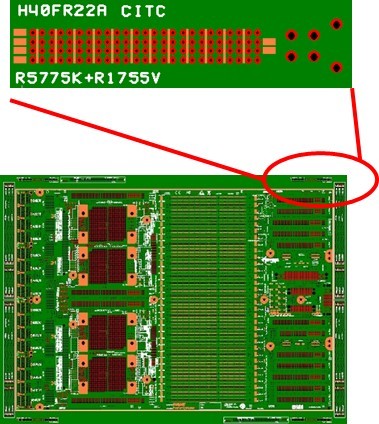

为了完成这项测试,在设计 PCB 板时就在边缘预留了一个条状测试电路,这种电路的内层走线与孔壁的连接以菊花链型实现。测试时先将测试电路从整个 PCB 板上裁剪下来,再在连线两端施加直流电压,由于整条电路的电阻只有 150 毫欧到 1.5 欧姆之间,对于直流电路来说相当于短路,大电流使得线路板发热升温,当温度达到指定要求后再迅速将其冷却到常温完成一个循环。每个循环结束后测量线路的电阻值并与初始时进行比较,如果阻值变化超过 10% ,则认为测试失败。

在普通 x86 服务器 PCB 的测试中,每个循环 5 分钟,其中加热 3 分钟,冷却 2 分钟,最高温度 150 摄氏度。 K1 Power 采用更为严苛的 CITC (Current Induced Thermal Cycling) 测试,加热、保持和冷却时间各 1 分钟,最高温度更是达到了 250 摄氏度。

K1 Power PCB 不仅是测试内容比 x86 更严格,测试标准也远高于 x86 PCB 。在 x86 上采用抽样测试,只要被抽样的测试条通过 6 个循环即被认为质量合格。 K1 Power PCB 则采用 100% 测试,每个测试条上都有一个编号,与 PCB 上的编号一一对应,质量合格的标准更高达 11 个循环,一旦某个测试条不能通过 11 个循环的测试,与之对应的 PCB 板将直接报废。

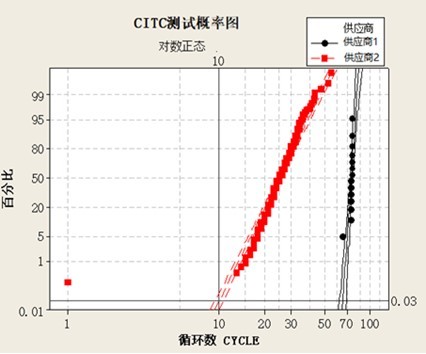

即使通过了 11 个循环后, PCB 的 CITC 测试还未结束。 K1 Power 的质量标准还要求进行极限测试,以便在统计学上实现故障率低于 300PPM (百万分之 300 )。因此在 K1 Power 的 CITC 测试中,每块测试条都是反复被测试直到阻值变化超过 10% 而导致测试失败,然后再根据成功通过测试的循环数量进行统计计算。

统计计算是假设测试条能通过的最大循环数满足标准正态分布。我们知道在正态分布下,均值加减 3 倍标准差所覆盖的区间内能覆盖 99.7% 的样本,或者说样本出现在正负 3 倍标准差区间之外的可能性小于 0.3% ,这也是大多数现代企业采用的质量标准。 K1 Power 的质量要求是 300PPM ,也就是 0.03% ,比 3 倍标准差的要求还要严格一个数量级!为了实现这一点,每块测试条能够通过测试的循环数要远高于 11 。如上图所示,供应商 2 的产品虽然在 CITC 测试中都坚持了 11 个循环,但由于加工稳定性较差,标准差比较大,在概率计算时还是有可能达不到 300PPM 。在 K1 Power 的质量标准里,如果一批 PCB 在进行概率计算后达不到 300PPM ,那整批 PCB 也要报废,与此同时,还会限制工厂继续生产,进行问题排查和整改。

五、总结

上面谈到的从选材、设计、工艺和测试,没有任何一项 x86 服务器不能采用,但到目前为止,只有 K1 Power 服务器采用了所有这些技术,归根结底还是成本问题。

业界普遍公认, PCB 成本随 PCB 层数增加呈指数级增长, K1 Power 高达 40 层的 PCB 其成本比 X86 高端服务器 20 层的 PCB 成本差距高达 11.6 倍!

抛开直接成本外,由于加工难度的提升, K1 Power 主板 PCB 的加工周期也比普通服务器 PCB 的耗时长,对整个供应链的要求也更高。可是 K1 Power 并没有因为这些直接或间接的成本提高就放弃对高品质的追求,而这些在细节上的精益求精更是造就了 K1 Power 的高可靠性!

如果觉得我的文章对您有用,请点赞。您的支持将鼓励我继续创作!

赞2

添加新评论0 条评论